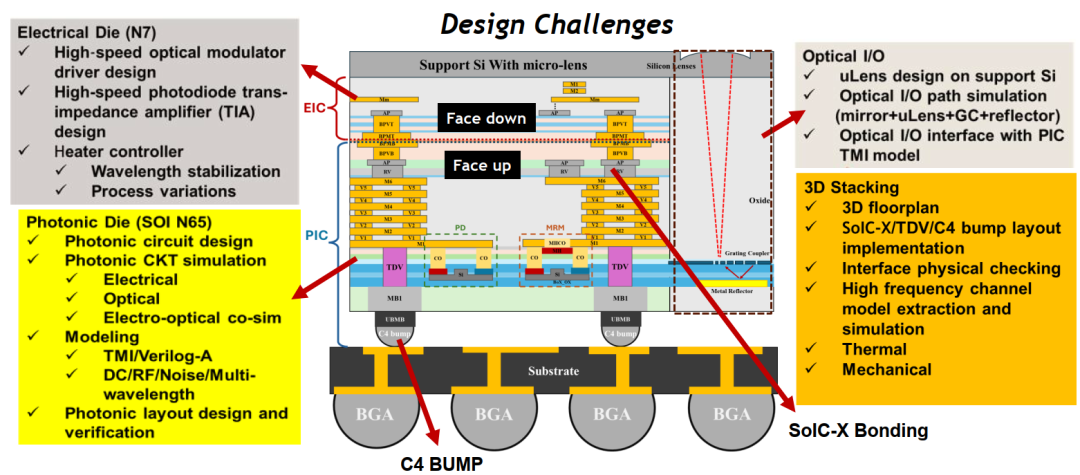

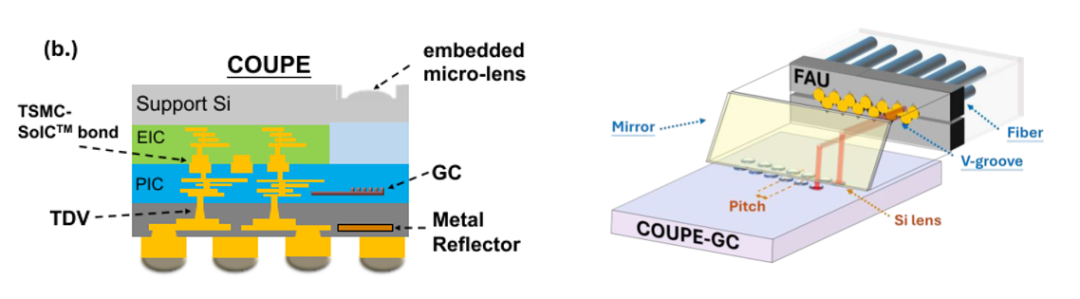

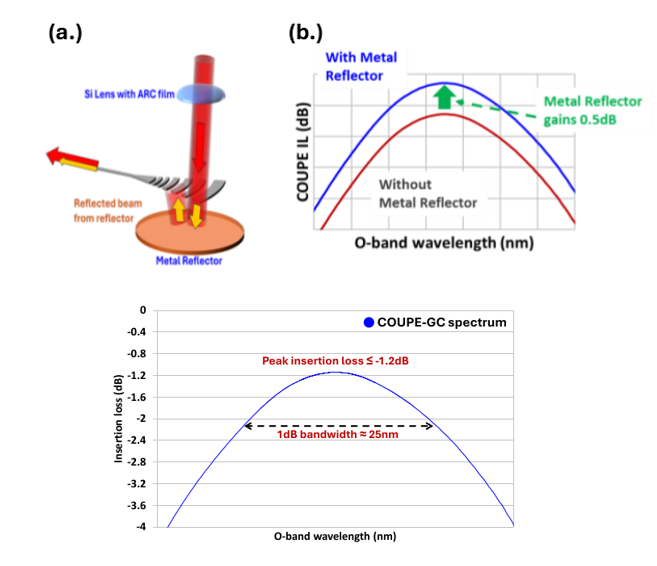

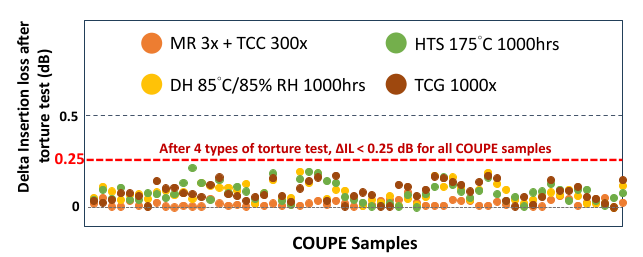

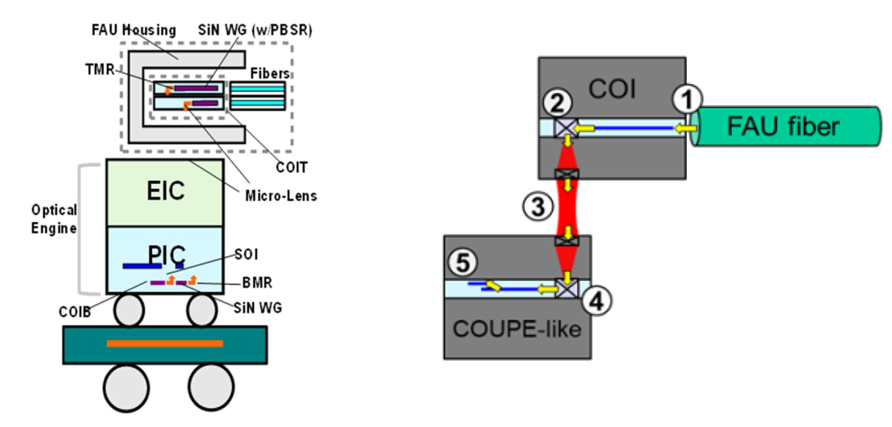

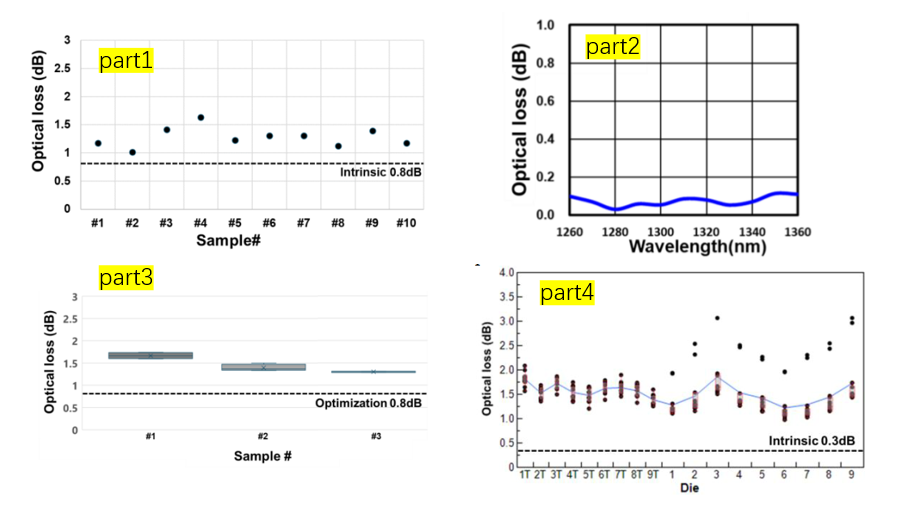

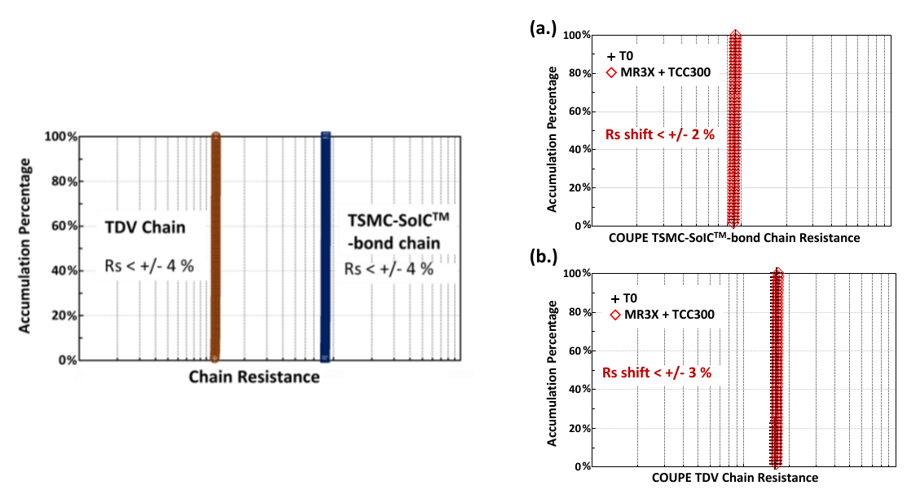

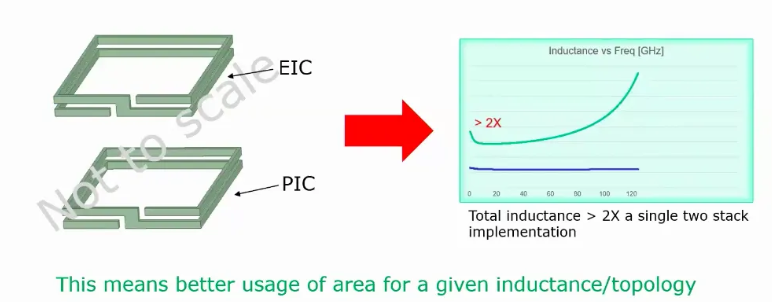

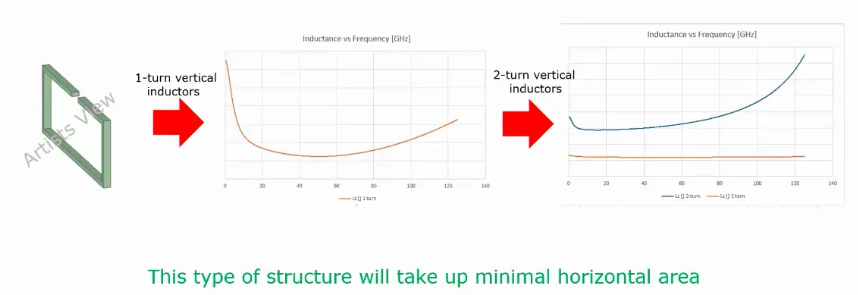

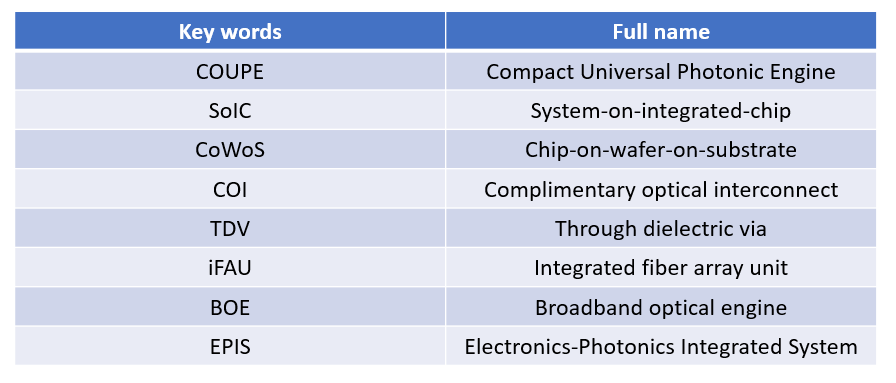

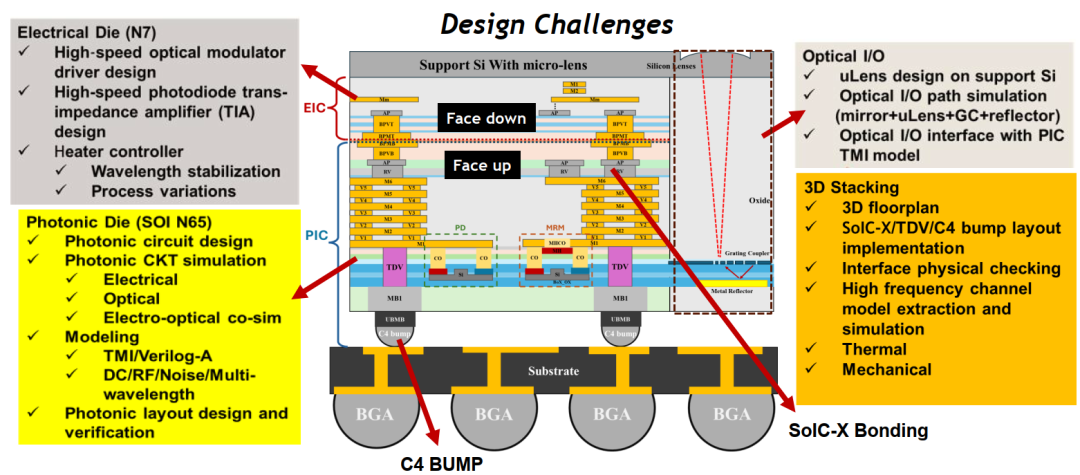

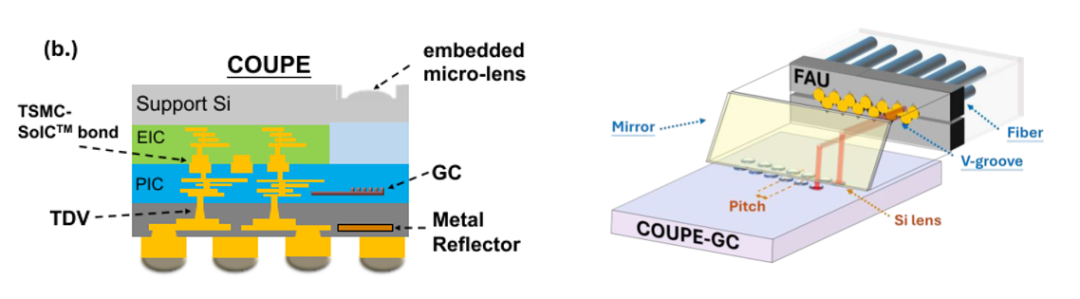

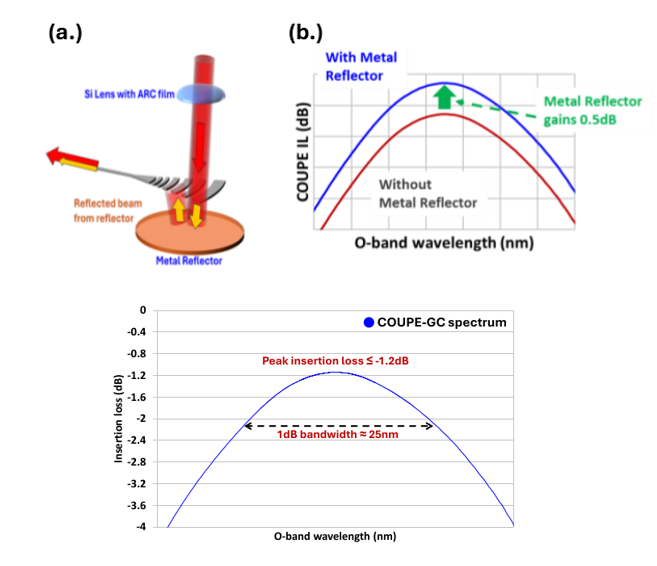

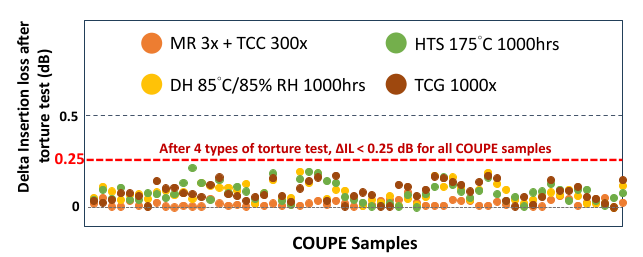

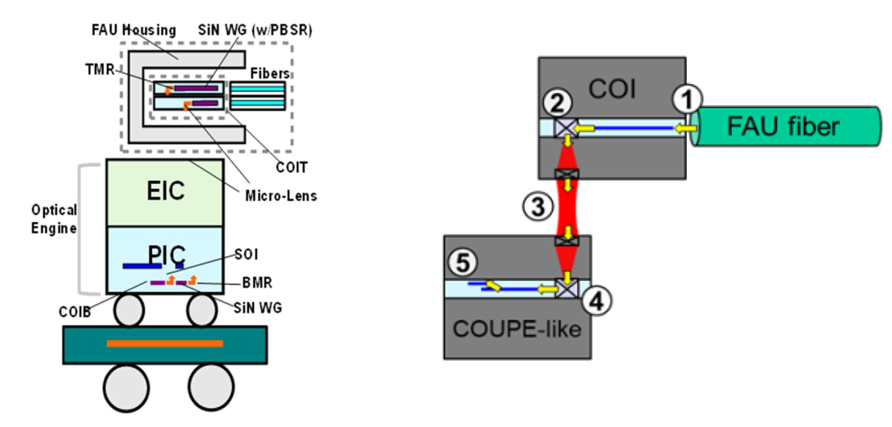

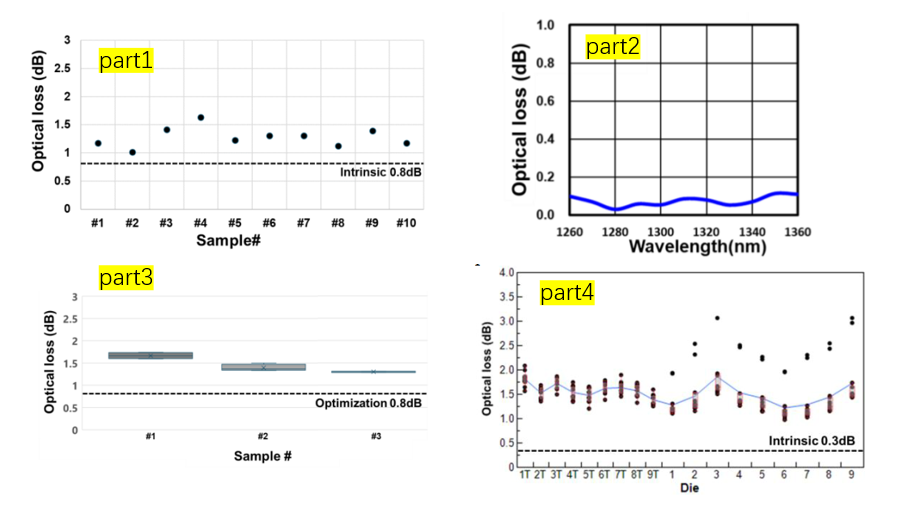

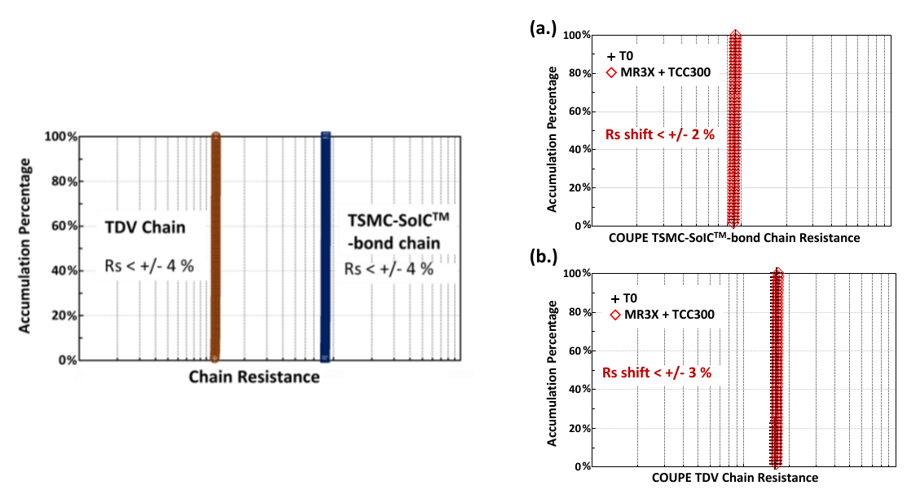

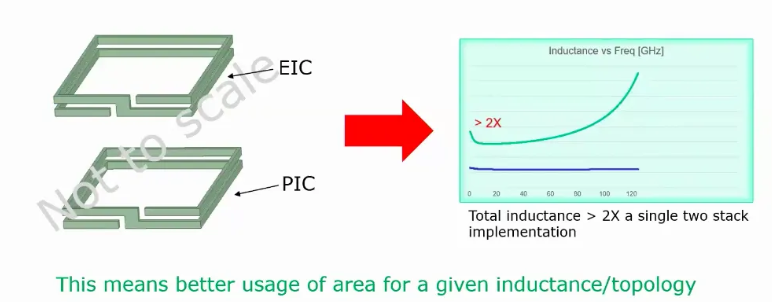

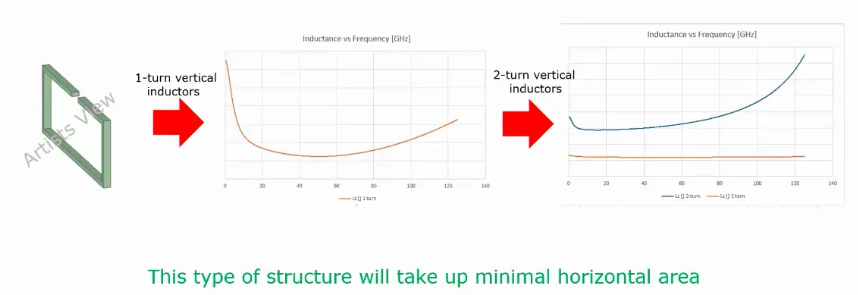

TSMC在今年的OFC、ECTC、VLSI等大會上先后報道了其硅光平臺的最新進展,包括不同耦合方案的技術細節與實測結果,展示了其COUPE平臺的技術優勢與發展方向。小豆芽這里匯總下相關信息,方便大家參考。從上述頂會的分類也可以看出,臺積電硅光平臺的研發涉及光學、封裝、電學等方向。臺積電內部是由多個團隊在共同開發硅光平臺,在不同文章中涉及到多個關鍵詞,這里先統一羅列出來,方便后續的閱讀。COUPE平臺的cross-section如下圖所示,PIC的substrate被去除掉,芯片只剩下幾微米厚,并且在PIC內加工出TDV, 用于電信號在垂直方向的傳輸。PIC內含有6層金屬(一般硅光平臺為兩層金屬),走線資源比較豐富,并在光柵耦合器對應的背面位置處加工出一層反射金屬,用于提高其耦合效率。EIC與PIC通過hybrid-bonding的方式集成在一起(SoIC bonding)。由于EIC-PIC混合集成后的die厚度較小,需要在EIC背面鍵合一個輔助的硅片, 其厚度為800um,用于解決芯片的翹曲問題。此外,在硅片上表面還可以加工出微透鏡結構,對光柵耦合器發出的光束進行整形。COUPE的光柵耦合方案,如下圖所示,利用PIC背面的金屬層作為反射層(metal reflector),增加GC的耦合效率。在硅片表面加工出微透鏡結構,對光束進行整形。光束傳播到片外后,再借助于反射鏡將光束偏折到水平方向,進入到光纖陣列(FAU)中。反射鏡可以將不同位置的光束都反射到同一個FAU不同高度的光纖中,從而實現多排光纖的耦合,提高帶寬密度。該雙排FAU也是由TSMC加工。引入背面的metal reflector后,光柵的耦合效率可提高約0.5dB, 如下圖所示。由于輔助硅片的厚度較厚,需要精心設計光柵的發射角、微透鏡的曲率、多層抗反射膜的厚度等。最終,整個光柵耦合方案的耦合損耗為1.2dB, 1dB帶寬為25nm。引入微透鏡與反射鏡這些光器件后,并沒有導致光柵耦合損耗的降低,1dB帶寬提高了5nm。依賴于TSMC良好的工藝控制能力,整個wafer內GC的中心波長可以控制在1.7nm以內。進一步,TSMC對該耦合方案進行了可靠性測試實驗,測試項包括DH(damp heat,高溫高濕)、HTS(high temperature storage, 高溫存儲測試)、MR(multi-reflow, 多次回流焊)和TC(temperature cycling, 熱循環)等。測試結果如下圖所示,耦合損耗整體的劣化小于0.25dB。在去年的IEDM會議上(TSMC硅光平臺COUPE的最新進展),TSMC公布過edge coupler相關的耦合方案細節,今年的ECTC會議上則展示了更多的測試結果,小豆芽此前對一些數據的疑惑可以得到解釋。為了與GC方案加以區分,TSMC將edge coupler的解決方案命名為EPIS-BOE(Electronics-Photonics Integrated System, Broadband Optical Engine)。BOE可以拆解為5個光學界面,如下圖所示:part1為FAU與COI中的SiN波導耦合;part2為COI中光從SiN波導傳播到advanced coupler(棱鏡),傳播方向從水平變為豎直方向;part3中光從COI進入到自由空間,通過透鏡進入到COUPE; part4為COUPE平臺中繼續利用advanced coupler偏折光束,光的傳播方向變為水平方向;part5中光通過PIC背面多層SiN波導的傳遞,進入到PIC芯片內。關于advanced coupler, TSMC沒有公布具體的結構信息,但提及到使用N28工藝加工制造,應該是刻蝕出的棱鏡結構。iFAU組件是TSMC利用12寸Si工藝線制造出來的,iFAU與COI均含有40組通道。TSMC依次對這5部分的光學損耗進行了表征,需要注意的是,去年IEDM會議上報道的0.1dB耦合損耗,只是針對part1界面使用單根光纖與COI中的SiN波導進行耦合的場景,而不是BOE方案的整體耦合損耗。由于part5是光從多層SiN波導轉移到Si波導,其損耗較小,可以控制在0.01dB上下。其它四部分的插損結果,如下圖所示。受限于不同通道間fiber工藝的偏差,part1中的loopback結構耦合插損為1.28±0.18dB。Part2的平均損耗為0.09dB。Part3的測試樣本較少,只有三個樣品的數據,其損耗分別為1.66dB、1.39dB和1.30dB。損耗較大的原因與advanced coupler的表面加工質量、微透鏡的表面加工質量、對準的精度等因素相關。Part4的損耗也比較大,共測試了18組樣品,平均插損在1.5dB上下,同樣也是受限于advanced coupler的表面加工質量。5個部分合計的損耗在4.33dB上下,性能較差。通過工藝的優化迭代,part1的損耗預期可以優化到0.8dB,part3可以優化到0.8dB,part4可以優化到0.3dB,整個BOE方案的光口方案有望實現在1260-1360nm波段內2dB的損耗指標。損耗的主要因素為多通道FAU、advanced coupler、micro lens等光學組件的表面加工偏差。TSMC的COUPE平臺使用了TDV和hybrid-bonding這兩項技術,有效減小了金屬互聯的寄生參數。TDV和hybrid-bonding電阻的阻值偏差可以控制在4%以內,而在MR+TC的可靠性實驗中,hybrid-bonding的電阻阻值變化2%,TDV阻值變化3%。Hybrid-bonding為光電混合系統提供了新的設計思路,TSMC報告中列舉了幾個典型的場景:1) TIA與PD之間,driver與modulator間的金屬長度縮短,降低了這部分電學連接對系統RF性能的影響2) 可以充分利用PIC與EIC的金屬資源,達到想要的設計效果,例如同樣的芯片面積可實現更大的電感,如下圖所示3) 可以實現豎直方向的電感,減小芯片面積,如下圖所示以上是對TSMC硅光平臺最新消息的匯總,目前TSMC光柵耦合方案的損耗為1.2dB, 主要通過背面的metel reflector和micro lens來提高耦合效率與耦合對準的容差,耦合損耗在可靠性實驗中會劣化約0.25dB。而端面耦合方案的損耗目前是4.33dB, 未來通過優化advanced coupler與micro lens表面加工的質量,有望降低到2dB以下。BOE方案中涉及到的光學組件,包括advanced coupler、micro-lens、iFAU等,都是由TSMC在不同的節點工藝下晶圓級加工出來,充分發揮其強大的加工能力。無論是grating coupler還是edge coupler方案, 當前展示的都是中間產物,其最終的目的還是為了實現CPO的可插拔光連接器,引入了微透鏡和iFAU, 后續實現可插拔的功能難度上不會很大。此外,兩種耦合方案都支持多排光纖陣列,有效提高了光學帶寬密度。在金屬互聯方面,由于采用TDV和hybrid-bonding技術,寄生參數比傳統方案減小了不少,可支持更高速率的互聯,另外可以充分利用EIC與PIC的金屬資源,引入一些新型的3D器件設計,有效利用芯片面積。臺積電也在積極探索MRM相關的電路設計,已經有一些初步結果。

1. Frank J.C.Lee, "3D Optical Interconnect Design", VLSI Symposium 2025.2. M. F. Chen, et.al., "Optical and Electrical Characterization of A Compact Universal Photonic Engine", ECTC 2025.3. K. H. Luo, et.al., "Broadband Optical Engine System Integration by

Wafer Level Process in HPC/AI Era", ECTC 2025.