【布局】OpenAI年底上線超100萬個GPU

關鍵詞: OpenAI FuriosaAI 3D-IC AI芯片 電機磁體

1.Sam Altman:OpenAI年底上線超100萬個GPU;

2.韓國AI芯片創(chuàng)企FuriosaAI斬獲LG大單;

3.破局 AI 算力困局:3D-IC 技術架構的顛覆性變革;

4.日本Proterial開發(fā)無需重稀土的電動汽車電機磁體,已發(fā)貨樣品;

1.Sam Altman:OpenAI年底上線超100萬個GPU;

OpenAI首席執(zhí)行官Sam Altman在X上的一篇新文章中透露,OpenAI有望在今年年底前“上線超過100萬個GPU”。

對比之下,埃隆馬斯克的xAI在今年早些時候憑借其Grok 4模型引起轟動,該模型運行在大約20萬個英偉達H100 GPU上。

OpenAI的計算能力是Grok 4模型的5倍,但對于Altman來說這還不夠。“為團隊感到非常自豪......”他寫道,“但現(xiàn)在他們最好開始研究如何將其提高至100萬個GPU的100倍。”

早在2月份,Altman就承認OpenAI不得不放慢GPT-4.5的推出速度,因為他們實際上“GPU 用完了”。這可不是小問題;考慮到英偉達的頂級AI硬件到明年的訂單也已售罄,這可謂一記警鐘。此后,Altman將計算擴展作為首要任務,尋求合作伙伴關系和基礎設施項目。

按照目前的市場價格,1億塊GPU的成本約為3萬億美元——幾乎相當于英國的 GDP,這還不包括電力需求或容納這些GPU所需的數(shù)據(jù)中心。英偉達短期內(nèi)根本不可能生產(chǎn)出這么多芯片,更不用說滿足所有GPU的能源需求了。

OpenAI并非僅僅囤積英偉達硬件。雖然微軟的Azure仍然是其主要的云服務骨干,但OpenAI 已與甲骨文合作構建自己的數(shù)據(jù)中心,并且據(jù)傳正在探索谷歌的TPU加速器,以使其計算堆棧多樣化。這是一場更大規(guī)模軍備競賽的一部分,從Meta到亞馬遜,每家公司都在自主研發(fā)AI芯片,并大力投資高帶寬內(nèi)存(HBM),以支持這些龐大的模型。Altman則暗示了OpenAI自己的定制芯片計劃,考慮到公司不斷增長的規(guī)模,這并非偶然。(校對/李梅)

2.韓國AI芯片創(chuàng)企FuriosaAI斬獲LG大單;

韓國AI芯片創(chuàng)企FuriosaAI致力于設計芯片與英偉達競爭,在拒絕Meta Platforms的8億美元收購要約數(shù)月后,終于簽下首份重要合同。

經(jīng)過七個月的嚴格評估,這家初創(chuàng)公司的AI芯片RNGD最終獲得LG AI Research的批準,該芯片涵蓋性能和效率。FuriosaAI CEO June Paik表示,LG將使用該芯片為其Exaone大型語言模型提供支持。

作為合作的一部分,F(xiàn)uriosaAI和LG計劃利用Exaone在從電子到金融等多個行業(yè)部署RNGD服務器。這些服務器還將為LG的內(nèi)部企業(yè)AI代理ChatExaone提供支持,LG計劃將其擴展到外部客戶。

LG的批準是對FuriosaAI的肯定,F(xiàn)uriosaAI是少數(shù)幾家希望在后ChatGPT時代AI基礎設施繁榮發(fā)展中分一杯羹的韓國芯片設計公司之一。 RNGD芯片的設計初衷不僅是為了挑戰(zhàn)行業(yè)領導者英偉達,也是為了挑戰(zhàn)其他初創(chuàng)公司,例如Groq、SambaNova Systems和Cerebras Systems。

今年3月,F(xiàn)uriosaAI拒絕了Meta的收購要約,選擇獨立運營,此舉引發(fā)公眾關注。據(jù)知情人士透露,F(xiàn)uriosaAI計劃在最終進行首次公開募股(IPO)之前進行融資。

FuriosaAI由曾在三星電子和AMD公司工作的June Paik于2017年創(chuàng)立,致力于開發(fā)用于AI推理或服務的半導體。該公司聲稱,其每瓦推理性能比圖形處理器(GPU)提高2.25倍。

與韓國同行Rebellions和Semifive一樣,F(xiàn)uriosaAI正試圖利用過去十年圍繞三星等公司涌現(xiàn)的龐大的半導體生態(tài)系統(tǒng),其中包括人才、供應商和政府激勵措施。

FuriosaAI正在努力爭取美國、中東和東南亞地區(qū)的新客戶。June Paik表示,預計今年下半年將達成類似協(xié)議。(校對/趙月)

3.破局 AI 算力困局:3D-IC 技術架構的顛覆性變革;

AI 時代的數(shù)據(jù)洪流與算力瓶頸

從日常生活中的語音助手和自動駕駛,到工業(yè)上的全自動工廠和 AI 輔助設計,人工智能技術正在為我們的世界帶來革命性的變化。在人工智能的應用中,無論是文字、語音、還是視頻,都需要被轉化為一串串的基本的數(shù)據(jù)單元,以供 AI 處理器識別并進行運算處理。這些單元被稱之為 token。

現(xiàn)代的 AI 系統(tǒng)往往要面臨同時產(chǎn)生的海量 token 輸入,并且需要在一秒內(nèi)完成十億甚至百億數(shù)量級的 token 處理。這種高并發(fā)、高帶寬的需求對計算機架構和芯片的設計提出的新的挑戰(zhàn):在搭載于傳統(tǒng)的二維芯片上,尤其是使用馮·諾伊曼結構的計算機中,處理器與內(nèi)存之間的總線好比鄉(xiāng)間雙向二車道的小路,數(shù)據(jù)傳輸速率和帶寬十分有限,已經(jīng)遠不能承載 AI 時代的數(shù)據(jù)洪流。數(shù)據(jù)顯示,當前 AI 芯片的算力利用率通常低于 30%,其主要原因正是處理器與內(nèi)存之間數(shù)據(jù)傳輸速率與帶寬跟不上處理器的運算速度。這種被稱為“內(nèi)存墻”的現(xiàn)象已經(jīng)成為了限制 AI 系統(tǒng)性能的瓶頸。

3D-IC——突破維度的技術革命

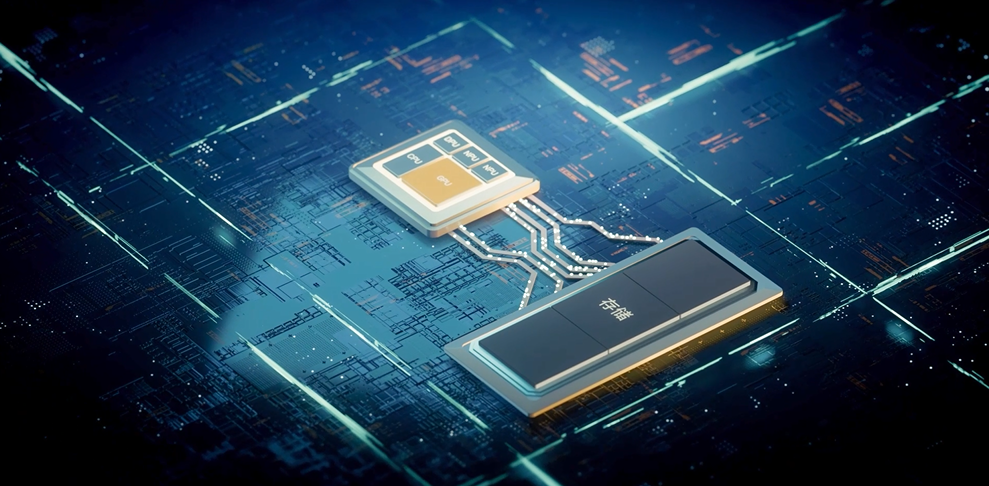

為了解決“內(nèi)存墻”對 AI 系統(tǒng)的桎梏,當今主流的 AI 芯片大多采用了2.5D 的方式設計制造。2.5D 就是將存儲和運算芯片擺放在同一平面上,借助平面下方的中介層傳輸芯片來實現(xiàn)千和萬數(shù)量級的連接,初步解決了存儲和運算之間數(shù)據(jù)通路擁塞的問題。此外,將傳統(tǒng)的大芯片切分為更小的存儲和運算芯片后,良品率也能得以大幅提升。但如果要滿足更嚴苛的高并發(fā)、高帶寬的需求,我們就需要升級到 3D 的設計,將存儲芯片直接堆疊在運算芯片之上。

在 3D-IC 的工藝中,金屬微凸塊(micro bump)或復合鍵(hybrid bonding)可以將上下堆疊的兩個芯片直接連接。如有信號需要穿過整層芯片,則可以通過硅通孔(TSV)穿過芯片的硅襯底、器件層、甚至金屬層。3D-IC 結構下的芯片間垂直互連進一步縮短了數(shù)據(jù)傳輸距離,從而提高了數(shù)據(jù)傳輸速率,減小了傳輸功耗。由于芯片的整個接觸面都可以擺放連接接口,芯片間并行連接的數(shù)量得以有極大的增加,帶寬可由此得到若干個數(shù)量級的提高。以上將內(nèi)存和運算放在一起的結構被稱為近存運算,是當前打破“內(nèi)存墻”的重要手段。

最先進的芯片設計者甚至會在面對不同運算需求時,平衡運算性能和設計制造成本,同時采用 2.5D 和 3D 的連接技術,即 3.5D 芯片。3.5D 的設計可以更好地支持異構運算以及處理海量數(shù)據(jù)。

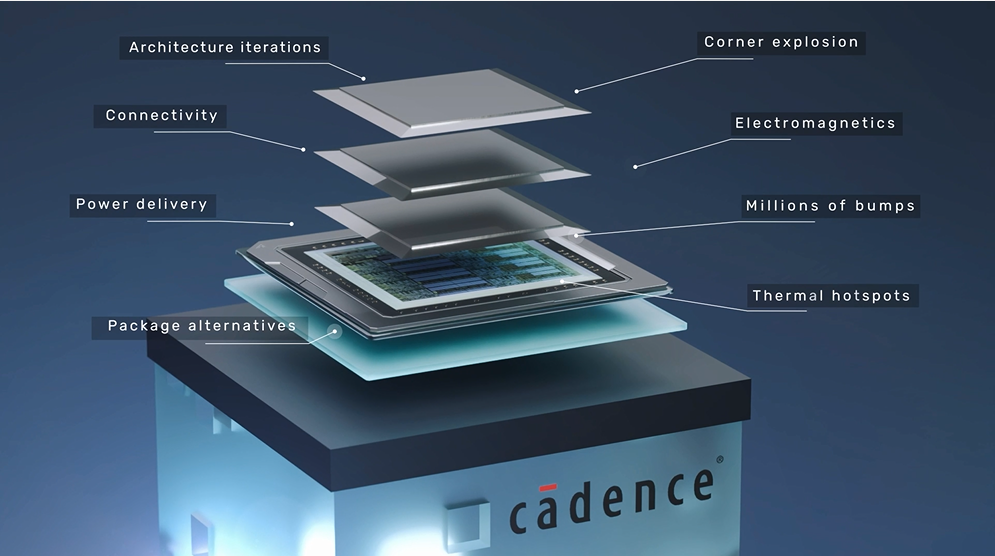

Cadence Integrity 3D-IC——全流程設計平臺

3D-IC 的設計不同于傳統(tǒng)的封裝設計和芯片設計,需要創(chuàng)新的設計方法學和工具的支持。傳統(tǒng)的先進封裝流程會先由封裝決定每個芯粒的接口,之后將設計目標拆分給芯片設計團隊。然而這樣的流程無法實現(xiàn)跨芯片、芯片與封裝之間的系統(tǒng)級優(yōu)化。3D-IC 的設計需要把傳統(tǒng) 2D 芯片中的性能、功耗、面積、成本(PPAC)指標驅動的設計拓展到整個 3D 系統(tǒng)中。

Cadence 致力于提供軟件、硬件和 IP 產(chǎn)品,助力電子設計概念稱為現(xiàn)實。基于此,Cadence 率先推出了能在在單一平臺上實現(xiàn) 3D-IC 全流程的 EDA 軟件——Integrity 3D-IC,給業(yè)界提供了一套完整的 3D-IC 解決方案。該方案支持所有 3D-IC 設計類型和各種工藝節(jié)點,并讓 3D-IC 設計的各個部門通過 Cadence 的數(shù)字設計平臺 Innovus、模擬及定制化設計平臺 Virtuoso 和封裝與板級設計平臺 Allegro 實現(xiàn)全系統(tǒng)跨平臺的無縫協(xié)作。為了達到更好的 3D 系統(tǒng)的設計效果,Integrity 3D-IC 將 3D-IC 的設計流程拆分為:

早期架構探索 – 探索分析不同的 3D 堆疊架構,快速進行方案迭代。優(yōu)化 bump 和 TSV 的規(guī)劃與擺放。

中期設計實現(xiàn) – 3D 系統(tǒng)的 partition 與floorplanning,3D placement、CTS、routing 及優(yōu)化,跨芯片的靜態(tài)時序分析與收斂。

后期多物理場簽核 – 包括對 3D-IC 簽核至關重要的系統(tǒng)級熱分析、電源分配網(wǎng)絡分析,3D 系統(tǒng)的信號完整性與電源完整性,3D 靜態(tài)時序分析等多物理場的簽核,系統(tǒng)級的 LVS 和 DRC。

從而使 3D-IC 芯片的堆疊、互聯(lián)以及各芯粒都能根據(jù)全系統(tǒng) PPAC 的最優(yōu)或次優(yōu)解完成規(guī)劃與實現(xiàn),讓芯片公司設計出更有競爭力的 3D-IC 產(chǎn)品。

未來展望:3.5D 異構集成時代

在半導體產(chǎn)業(yè)邁向新征程的關鍵節(jié)點,Cadence 始終以創(chuàng)新者的姿態(tài)深耕行業(yè)前沿。面向未來,Cadence 滿懷熱忱與期待,愿與行業(yè)合作伙伴同心同行,共同推動下一代 3.5D 的技術創(chuàng)新。這不僅是技術參數(shù)上的迭代升級,更是對芯片設計方法學的深度重塑,力求為行業(yè)發(fā)展注入新動能。

Unleash your imagination,與 Cadence 攜手,將創(chuàng)意變成現(xiàn)實!

4.日本Proterial開發(fā)無需重稀土的電動汽車電機磁體,已發(fā)貨樣品;

日本金屬制造商Proterial開發(fā)出無需使用重稀土金屬的電動汽車電機磁體,這一突破有望緩解中國限制此類材料出口帶來的供應鏈擔憂。

Proterial(前身為日立金屬)開發(fā)出兩種釹磁體,因其高性能,可用于精密機器和電動汽車。該公司已開始從其量產(chǎn)工廠發(fā)貨一種磁體的樣品。第二種具有更高耐熱性的磁體樣品預計最早將于2026年4月開始發(fā)貨。

中國于今年4月對稀土金屬實施出口限制,引發(fā)了國際社會對供應鏈的擔憂。日本汽車制造商鈴木汽車公司因稀土短缺于5月停產(chǎn)其Swift緊湊型轎車。廣泛采用不使用重稀土金屬的磁體可以減少供應鏈不穩(wěn)定。

釹磁體可用于縮小電動汽車電機的尺寸,但需要添加鋱和鏑等重稀土元素才能提高耐熱性。Proterial的新技術使其能夠在不使用重稀土元素的情況下保持高性能。

這些新型磁體可以輕松應用于現(xiàn)有電機。它們采用主流生產(chǎn)工藝制造,使用現(xiàn)有的產(chǎn)線生產(chǎn),并且支持進行形狀調(diào)整以適應各種類型的電機,方便以低成本進行量產(chǎn)。

Proterial并非首家開發(fā)不含重稀土元素的釹磁體公司。Daido Steel也開發(fā)出用于電動汽車電機的類似磁體,但這些磁體需要調(diào)整電機的形狀和冷卻方式,以匹配使用重稀土元素的磁體的輸出功率。